# HT82V842 CCD CDS/PGA/10b-20M-ADC

## **Features**

- Operating voltage: 2.7V~3.6V

- Low power consumption: 70mW (Typ.)

- Power down mode: less than 30μW

- Accepts a direct signal input to ADC or PGA at 1.0 V<sub>PP</sub> (Typ.)

- CCD signal input level: 1.1 V<sub>P-P</sub> (Max.)

- 10-bit ADC (up to 20MHz)

- DNL: ±0.6 LSB (Typ.)

- Black level neutralizer, target setting: 16~127LSB

- · Built-in serial interface

- Independent ADC input conversion clock and data output clock

- · Independent CDS and PGA gain control

- CDS: -1.94/0/6/12dB

- PGA: 0~24dB

- Wide gain range: -1.94~36dB

- High speed sample and hold circuit: pulse width 11ns (Min.)

- 48-pin LQFP package

# **General Description**

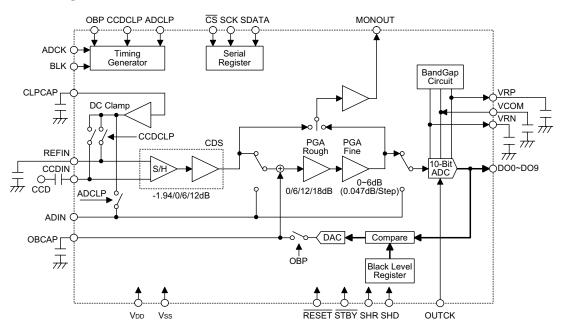

The HT82V842 is a CMOS single-chip signal processing device for CCD area sensors. It consists of a clamp circuit, Correlated Double Sampler (CDS), Programmable Gain Amplifier (PGA), reference voltage generator,

black level detection circuit, 20MHz 10-bit A/D converter (ADC), timing generator for internally required pulses, serial interface for internal function control and PGA gain control.

# **Block Diagram**

Rev. 1.00 1 July 15, 2004

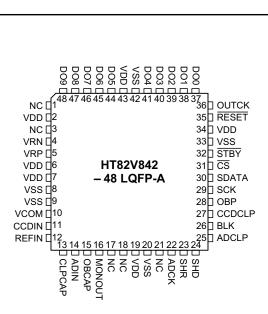

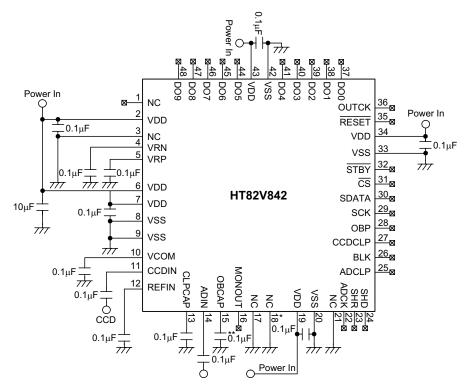

# **Pin Assignment**

# **Pin Description**

| Pin No.            | Pin Name | I/O | Description                                                                               |

|--------------------|----------|-----|-------------------------------------------------------------------------------------------|

| 1, 3, 17~18, 21    | NC       | _   | No connection                                                                             |

| 2, 6~7, 19, 34, 43 | VDD      | _   | Positive power supply for analog circuit                                                  |

| 4                  | VRN      | 0   | Negative reference voltage for internal ADC Connect to $V_{SS}$ via $0.1 \mu F$           |

| 5                  | VRP      | 0   | Positive reference voltage for internal ADC Connect to $V_{SS}$ via $0.1 \mu F$           |

| 8~9, 20, 33, 42    | VSS      | _   | Negative power supply for analog circuit                                                  |

| 10                 | VCOM     | 0   | Common reference voltage for internal ADC                                                 |

| 11                 | CCDIN    | ı   | CDS circuit data input                                                                    |

| 12                 | REFIN    | ı   | CDS circuit reference input                                                               |

| 13                 | CLPCAP   | 0   | Clamp level output Connect to V <sub>SS</sub> via 0.1μF                                   |

| 14                 | ADIN     | ı   | ADIN signal input                                                                         |

| 15                 | ОВСАР    | 0   | Black level integration voltage Connect to $V_{SS}$ via $0.1 \mu F^{1}$ (by applications) |

| 16                 | MONOUT   | 0   | Monitor output of CDS or PGA                                                              |

| 22                 | ADCK     | ı   | ADC sampling clock input                                                                  |

| 23                 | SHR      | ı   | Reference sampling pulse input                                                            |

| 24                 | SHD      | ı   | Data sampling pulse input                                                                 |

| 25                 | ADCLP    | ı   | Pulse input for ADIN clamp and black calibration control                                  |

| 26                 | BLK      | I   | Blanking pulse input                                                                      |

| 27                 | CCDCLP   | ı   | Clamp control input                                                                       |

| 28                 | OBP      | - 1 | Black level period pulse input                                                            |

| 29                 | SCK      | ı   | Serial clock input                                                                        |

| 30                 | SDATA    | I   | Serial data input                                                                         |

| 31                 | CS       | ı   | Serial port chip selection (Active at low)                                                |

| 32                 | STBY     | ı   | Power down control (Active low)                                                           |

| 35                 | RESET    | ı   | Reset signal (Active low)                                                                 |

| 36                 | OUTCK    | ı   | Clock source for ADC output                                                               |

| 37~41, 44~48       | DO0~DO9  | 0   | Digital output from ADC                                                                   |

# **Absolute Maximum Ratings**

| Supply Voltage | GND-0.3V to GND+6V               | Storage Temperature   | –55°C to 150°C |

|----------------|----------------------------------|-----------------------|----------------|

| nput Voltage   | $V_{SS}$ -0.3V to $V_{DD}$ +0.3V | Operating Temperature | –20°C to 70°C  |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# **D.C. Characteristics** Ta=25°C

| Symbol              | D                                    | Tes      | st Conditions                         |                    | Typ    | Max.               | 11               |

|---------------------|--------------------------------------|----------|---------------------------------------|--------------------|--------|--------------------|------------------|

| Symbol              | Parameter                            | $V_{DD}$ | Conditions                            | Min.               | Тур.   | wax.               | Unit             |

| $V_{IH}$            | High Level Input Voltage             | 3V       | _                                     | 0.7V <sub>DD</sub> | _      | $V_{DD}$           | V                |

| $V_{IL}$            | Low Level Input Voltage              | 3V       | _                                     | 0                  | _      | 0.3V <sub>DD</sub> | V                |

| l <sub>IH</sub>     | High Level Input Current             | 3V       | V <sub>IL</sub> =0V                   | _                  | _      | 200                | μΑ               |

| I <sub>IL</sub>     | Low Level Input Current              | 3V       | V <sub>IH</sub> =3.0V                 | _                  | _      | 1                  | μА               |

| I <sub>MD</sub>     | Operation Current at Monitor Disable | 3V       | f <sub>S</sub> =20MHz                 | _                  | 23     | _                  | mA               |

| I <sub>MA</sub>     | Supply Current at Monitor Active     | 3V       | f <sub>S</sub> =20MHz                 | _                  | 26     | _                  | mA               |

| I <sub>SS</sub>     | Power Down Current                   | 3V       | _                                     | _                  | _      | 10                 | μА               |

| V <sub>CCDIN</sub>  | Analog Ingut Dange                   | 3V       | CCDIN input,<br>f <sub>IN</sub> =1MHz | _                  | 1.1    | _                  | V <sub>P-P</sub> |

| V <sub>ADIN</sub>   | Analog Input Range                   | 3V       | ADIN input,<br>f <sub>IN</sub> =1MHz  | _                  | 1.0    | _                  | V <sub>P-P</sub> |

| V <sub>CLPCAP</sub> | Clamp Voltage                        | 3V       | _                                     | 1.5                | 1.7    | 1.9                | V                |

| t <sub>BLKCAL</sub> | Black Calibration Time               | 3V       | _                                     | _                  | _      | 200                | Pixel            |

| V <sub>BLKCAL</sub> | Maximum Calibration Offset Voltage   | 3V       | _                                     | _                  | ±200   | _                  | mV               |

| G (0)               | CDS Gain (Set 0 dB)                  | 3V       | Absolute gain                         | -2                 | -1     | 0                  | dB               |

| G (1)               | CDS Gain (Set 6.02 dB)               | 3V       |                                       | 5.52               | 6.02   | 6.52               | dB               |

| G (2)               | CDS Gain (Set 12.04 dB)              | 3V       | Relative gain                         | 11.54              | 12.04  | 12.04              | dB               |

| G (3)               | CDS Gain (Set –1.94 dB)              | 3V       |                                       | -2.44              | -1.94  | -1.44              | dB               |

| Gmin                | PGA Gain (Minimum Gain)              | 3V       | Absolute gain                         | -1.2               | -0.2   | 0.8                | dB               |

| Gmax                | PGA Gain (Maximum Gain)              | 3V       | Polotivo goin                         | 22.906             | 23.906 | 24.906             | dB               |

| Gstep               | PGA Gain (Gain Step)                 | 3V       | Relative gain                         | 0                  | 0.047  | 0.094              | dB               |

| ER <sub>PA</sub>    | Total (CDS+PGA) Gain Monotony        | 3V       | _                                     | _                  | _      | ±4                 | LSB              |

| RES                 | Resolution                           | 3V       | _                                     | _                  | _      | 10                 | Bits             |

| DNL                 | Differential Nonlinearity            | 3V       | f <sub>S</sub> =20MHz                 | _                  | ±0.6   | ±1.0               | LSB              |

| SN                  | S/N                                  | 3V       | _                                     | _                  | 58     | _                  | dB               |

| SND                 | S/(N+D)                              | 3V       | _                                     |                    | 56     | _                  | dB               |

| V <sub>COM</sub>    | ADC Common Voltage                   | 3V       | _                                     | 1.25               | 1.4    | 1.55               | V                |

| $V_{RP}$            | V <sub>RP</sub> Voltage (Positive)   | 3V       | _                                     | 1.55               | 1.65   | 1.75               | V                |

| V <sub>RN</sub>     | V <sub>RN</sub> Voltage (Negative)   | 3V       | _                                     | 1.05               | 1.15   | 1.25               | V                |

| Sumb al           | Dovernator                              | Tes      | t Conditions | Min. | Тур. | Max. | I I mit |

|-------------------|-----------------------------------------|----------|--------------|------|------|------|---------|

| Symbol            | Parameter                               | $V_{DD}$ | Conditions   | win. |      | wax. | Unit    |

| C                 | ADC Output Block Lovel Colibration Code | 2),/     |              | 16   | _    | 127  | LSB     |

| C <sub>CAL</sub>  | ADC Output Black Level Calibration Code | 3V       | _            | 1    | _    | 127  | LSB     |

| ST <sub>CAL</sub> | Calibration Code Resolution             | 3V       | _            | _    | 1    | _    | LSB     |

Note: Black calibration period is specified when  $C_{CAL}$  is from 16 to 127LSB. Although black level codes of 1 to 15 could be set,  $t_{BLKCAL}$  is not guaranteed for these codes.

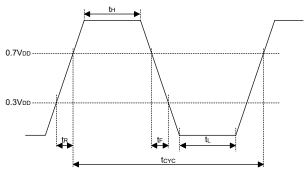

# A.C. Characteristics V<sub>SS</sub>=0V, Ta=25°C

|                     | _ ,                        |          | Test Conditions |      | _    |      |      |

|---------------------|----------------------------|----------|-----------------|------|------|------|------|

| Symbol              | Parameter                  | $V_{DD}$ | Conditions      | Min. | Тур. | Max. | Unit |

| f <sub>S</sub>      | Conversion Frequency       | 3.0V     | _               | 0.5  | _    | 20   | MHz  |

| t <sub>CYC</sub>    | Clock Cycle Time           | 3.0V     | _               | 50   | _    | _    | ns   |

| t <sub>R</sub>      | Clock Rising Time          | 3.0V     | _               | _    | _    | 2    | ns   |

| t <sub>F</sub>      | Clock Falling Time         | 3.0V     | _               | _    | _    | 2    | ns   |

| tL                  | Clock Low Period           | 3.0V     | _               | 23   | _    | _    | ns   |

| t <sub>H</sub>      | Clock High Period          | 3.0V     | _               | 23   | _    | _    | ns   |

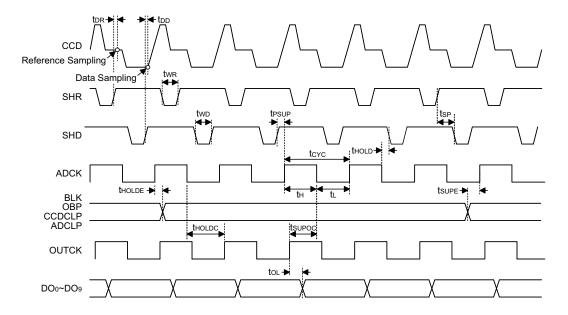

| t <sub>WR</sub>     | SHR Pulse Width            | 3.0V     | _               | 11   | _    | _    | ns   |

| t <sub>WD</sub>     | SHD Pulse Width            | 3.0V     | _               | 11   | _    | _    | ns   |

| t <sub>DR</sub>     | SHR Sampling Aperture      | 3.0V     | _               | _    | _    | 4    | ns   |

| t <sub>DD</sub>     | SHD Sampling Aperture      | 3.0V     | _               | _    | _    | 4    | ns   |

| t <sub>PSUP</sub>   | Data Pulse Setup           | 3.0V     | _               | 2    | _    | _    | ns   |

| t <sub>HOLD</sub>   | Data Pulse Hold            | 3.0V     | _               | 5    | _    | _    | ns   |

| t <sub>SP</sub>     | Sampling Pulse Non-overlay | 3.0V     | _               | 1    | _    | _    | ns   |

| t <sub>SUPE</sub>   | Enable Pulse Setup         | 3.0V     | _               | 10   | _    | _    | ns   |

| t <sub>HOLDE</sub>  | Enable Pulse Hold          | 3.0V     | _               | 10   | _    | _    | ns   |

| t <sub>SUPOC</sub>  | OUTCK Setup                | 3.0V     | _               | 0    | _    | _    | ns   |

| t <sub>HOLDOC</sub> | OUTCK Hold                 | 3.0V     | _               | 10   | _    | _    | ns   |

| t <sub>DLD</sub>    | 3-state Disable Delay      | 3.0V     | Active → High-Z | _    | 20   | _    | ns   |

| t <sub>DLE</sub>    | 3-state Disable Delay      | 3.0V     | High-Z→ Active  | _    | 20   | _    | ns   |

| t <sub>DL</sub>     | ADC Output Data Delay      | 3.0V     | _               | _    | 6    | _    | ns   |

## **Functional Description**

#### **CDS (Correlated Double Sampling) Circuit**

Connect the CCDIN pin to the CCD sensor thru a capacitor. Connect also the REFIN pin to  $V_{SS}$  thru a capacitor. The CDS circuit holds the pre-charge voltage of the CCD at SHR pulse and do sampling of the CCD pixel data at SHD pulse. Correlated noise is removed by subtracting the pre-charge voltage from the pixel data level. CDS could choose a gain setting from 0, 6.02, 12 or -1.94 dB (Mode 3, register D4 and D5 bits). A CDS gain is controlled by PGA gain. It is recommended to increase the CDS gain then increase the PGA gain to reduce the noise level.

## **Clamp Circuits**

· DC clamp

The DC level of the CCDIN/REFIN input is fixed by an internal DC clamp circuit. The DC level of the C-coupled CCD signal at the CDS input is set to CLPCAP by the internal DC clamp circuit. The clamp switches are usually turned on at the black level calibration period. The CLPCAP pin connects to  $V_{\rm SS}$  thru a  $0.1\mu F$  capacitor.

· ADIN signal clamp

Clamp operation can also be used for the ADIN path. The clamp voltage is different from the CCDIN/REFIN signal and it could be turned off by register setting. At "ADIN signal to ADC" mode, the ADCLP signal controls the "clamp circuit". Black level calibration circuit is also controlled by ADCLP at "ADIN signal to PGA" mode.

· Clamp control

Clamp current (Mode 2 register D7). Charge current can select normal or fast clamp.  Clamp target (Mode 2 register D5 and D4), input signals (REFIN and CCDIN) to be clamped are selectable. The clamp function can be turned off.

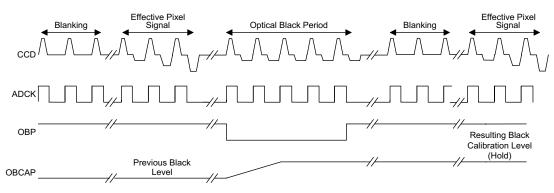

#### **Black Level Cancel Circuit**

The purpose of a black level cancel circuit is to control the DC level of the PGA input. The ADC output code at an optical black period may correspond to the black level code set up by the register. A black level code of (1 to) 16 to 127 LSB is available (the default is 64 LSB).

While the OBP pin is active a black level cancel loop is established. In the loop, a comparison is made between the ADC output code and the black level code, the result controls the voltage of the OBCAP capacitor. Hence, the OBCAP voltage settles gradually and the signal level of the optical black period corresponds to the established value.

The following conditions will reset the OBCAP capacitor:

- Set the black level reset register to "1" (Mode 1 register D1=1).

- Set the RESET pin to low

- Power down by STBY pin or register control

The DC clamping (CCDCLP) is allowed while the OBP pin is low. The black level cancellation is available at "ADIN signal to PGA" mode. The black level cancellation is available at the ADCLP period in this mode. The clamping function and black level canceling function are done simultaneously.

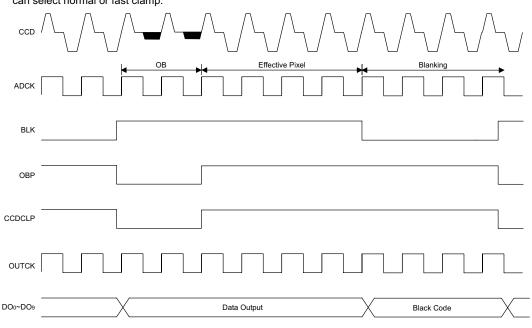

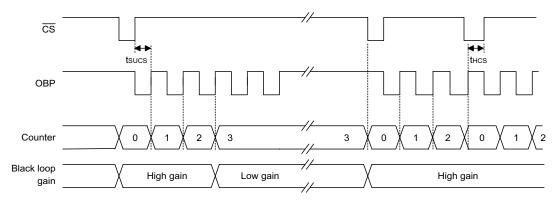

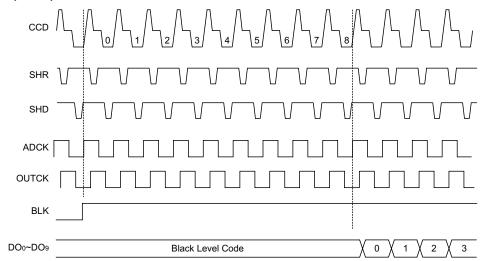

**Black Level Calibration Timing**

#### **High-speed Black Level Cancellation**

The HT82V842 has a high speed black level cancellation function, which by means of a register setting enhances the settling speed within a fixed period from access to the serial interface. It increases the gain of the setting DAC within a fixed period and in turn increases the charge/discharge current to the OBCAP capacitor.

The Mode 3 register D3 to D0 data controls the black level boost function. The default setting is always low

gain (D3~D0=5′b0). By setting the register D2~D0, the gain becomes high by 1 to 7 times that of the OBP pulse period after any access to the serial interface. After that period, the gain returns to low. When setting D3 to 1′b1, the gain is always high. The  $\overline{\text{CS}}$  signal becomes the starting point of the OBP pulse count.

The following figure shows the black loop settling gain boost timing chart when the boost control is on (D3="0") and the boost period is set to 3.

**Black Loop Settling Gain Boost Timing**

| Symbol            | Parameter     | Condition | Min. | Тур. | Max. | Unit |

|-------------------|---------------|-----------|------|------|------|------|

| t <sub>sucs</sub> | CS Setup Time | _         | 10   | _    | _    | ns   |

| t <sub>HCS</sub>  | CS Hold Time  | _         | 10   | _    | _    | ns   |

# **Gain Control Circuit**

The total gain for a CCD input signal covers from  $-1.94\,\mathrm{dB}$  to 36dB. The CDS range is  $0/6/12/-1.94\,\mathrm{dB}$ . The PGA rough is  $0/6/12/18\,\mathrm{dB}$  and ADC fine is 0 to 6dB,  $0.047\,\mathrm{dB/step}$ . The CDS gain is controlled by a 2-bit register and the PGA gain is controlled by a 9-bit register.

## A/D Converter Circuit

The HT82V842 includes one 20MHz 10 bits AD converter. The ADC converts the following signals.

- The signal from the CCDIN input through a CDS and PGA.

- The signal from the ADIN input through an PGA at the ADIN mode.

- The signal from the ADIN input at the ADIN mode.

## A/D Conversion Range

The analog input range of the ADC is determined by the internal reference voltage. The full scale of the ADC is  $1.0\ V_{PP}$ .

#### A/D Converter Output Code (Mode 1 Register D5=1)

The format of an ADC digital output is a straight binary. When in the input zero reference voltage, the output code will be all zero and when the input is a full scale voltage, the output code will be all one.

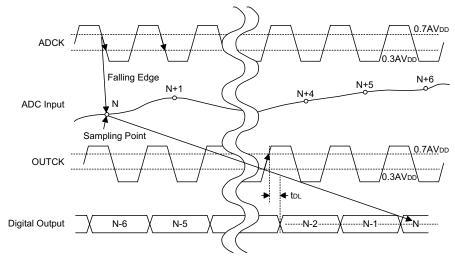

#### Clock, Pipeline Delay, Digital Data Output Timing

The ADCK input is used for an A/D conversion. The ADC input signal is sampled at the falling edge of the ADCK input and 10 bits parallel data is output at the ris-

ing edge of the ADCK input after a 5.5 clock of pipeline delay.

## **High-Z Control of ADC Digital Output**

ADC digital outputs become High-Z under the following conditions:

- Set the ADC output bit to one. (Mode 1 register D2=1)

- Set the STBY pin to low

- Set the power control bit to one (Mode 1 register D0=1)

|            |     | Digital Output Code |    |    |    |    |    |    |    |     |  |  |  |  |  |  |

|------------|-----|---------------------|----|----|----|----|----|----|----|-----|--|--|--|--|--|--|

| A/D Input  | MSB |                     |    |    |    |    |    |    |    | LSB |  |  |  |  |  |  |

|            | D9  | D8                  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |  |  |  |  |  |  |

| Full Scale | 1   | 1                   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   |  |  |  |  |  |  |

| ÷          | :   | :                   | :  | :  | :  | :  | :  | :  | :  | :   |  |  |  |  |  |  |

| i :        | 1   | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |  |  |  |  |  |  |

| ÷          | 0   | 1                   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   |  |  |  |  |  |  |

| :          | :   | :                   | :  | :  | :  | :  | :  | :  | :  | :   |  |  |  |  |  |  |

| Zero Scale | 0   | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |  |  |  |  |  |  |

ADC Data Output (Coding: Straight Binary)

# Miscellaneous Function (ADC Direct Input, ADIN Mode)

The direct input path to the ADC or the PGA is achieved by means of a register setting. The selectable paths are as follows:

- Function disable (default, Mode 1 register D5=0, D4=0)

- ADIN input to the PGA (Mode 1 register D5=0, D4=1)

- ADIN input to the PGA (Mode 1 register D5=1, D4=Don't care)

The BLK, SHD and SHR inputs are ignored at the ADIN mode.

#### **Power Down Mode**

The power down mode can be set either by register setting or by the  $\overline{\text{STBY}}$  pin.

#### **Monitor Output**

When setting Mode 2 (D1 and D0), the signal from MONOUT is selectable. The alternatives are OFF, CDS output, PGA output or REFIN/CCDIN output. The MONOUT pin gain is fixed to 0dB regardless of the gain control register setting when the CDS output is selected. The MONOUT level becomes  $V_{\text{COM}}$  at zero reference level. The signals are output in reverse for the CCD input.

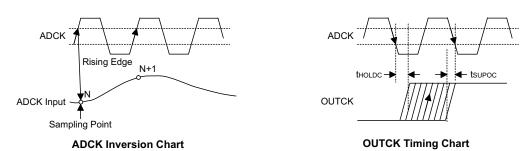

#### **Polarity Inversion**

The following input polarities can be inverted by register setting:

- ADCK (A/D converter sampling clock, Mode 1 register D6)

- SHR and SHD (CDS sampling clock, Mode 2 register D3 and D2)

- BLK, OBP, CCDCLP and ADCLP (Mode 2 register D3 and D2)

### **Data Output Clock**

The ADCK input or the OUTCK input is selectable as an ADC data output clock.

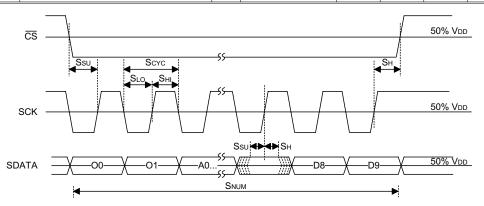

#### **Serial Interface Circuit**

The internal registers of the HT82V842 are controlled by a 3-wire serial interface. The data is a 16-bit length serial data that consists of a 2-bit operation code, 4 bits address and 10 bits data. Each bit is fetched at the rising edge of the  $\overline{\text{CS}}$  input. Keep  $\overline{\text{CS}}$  to high when not access HT82V842. It is prohibited to write to a non-defined address. When a data length is below 16 bits, the data is not executed.

#### Registers

The HT82V842 has 10 bits×7 registers that control the operations. All registers are write only, the serial registers are written by the serial interface.

| R/W   |    | Add | ress |    | Register Name   | Eurotion Description                                                                                     |

|-------|----|-----|------|----|-----------------|----------------------------------------------------------------------------------------------------------|

| IK/VV | А3 | A2  | A1   | A0 | Register Name   | Function Description                                                                                     |

| W     | 0  | 0   | 0    | 0  | Mode 1          | DOUT timing control/OUTCK polarity/ADCK polarity/ADIN connection/ADC output/Black level reset/Power down |

| W     | 0  | 0   | 0    | 1  | Mode 2          | Clamp current/ADIN clamp/Clamp target/S/H, enable logic/Monitor selection                                |

| W     | 0  | 0   | 1    | 0  | Mode 3/CDS gain | CDS gain control/Black loop gain boost/Boost period                                                      |

| W     | 0  | 0   | 1    | 1  | PGA gain        | PGA gain                                                                                                 |

| W     | 0  | 1   | 0    | 0  | Black level     | ADC code at black level (1 LSB step)                                                                     |

# Register Map

# Register Bit Assignment

|                       | D9 | D8 | D7 | D6       | D5 | D4 | D3 | D2 | D1 | D0 |

|-----------------------|----|----|----|----------|----|----|----|----|----|----|

| Mode 1                |    |    |    | •        |    |    | I  |    | ı  |    |

| Default               | Χ  | 0  | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  |

| Functions             |    |    |    |          |    |    |    |    |    |    |

| DOUT timing control   |    | √  |    |          |    |    |    |    |    |    |

| OUTCK polarity        |    |    | √  |          |    |    |    |    |    |    |

| ADCK polarity         |    |    |    | <b>√</b> |    |    |    |    |    |    |

| ADIN connection       |    |    |    |          |    |    |    |    |    |    |

| Reserved              |    |    |    |          |    |    | √  |    |    |    |

| ADC output            |    |    |    |          |    |    |    | √  |    |    |

| Black level reset     |    |    |    |          |    |    |    |    | √  |    |

| Power down            |    |    |    |          |    |    |    |    |    | √  |

| Mode 2                |    | 1  |    |          | 1  |    |    | I. |    |    |

| Default               | Х  | Х  | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  |

| Functions             |    |    |    |          |    |    |    |    |    |    |

| Clamp current         |    |    | √  |          |    |    |    |    |    |    |

| ADIN clamp            |    |    |    | √        |    |    |    |    |    |    |

| Clamp target          |    |    |    |          |    |    |    |    |    |    |

| S/H, enable logic     |    |    |    |          |    |    |    |    |    |    |

| Monitor selection     |    |    |    |          |    |    |    |    |    |    |

| Mode 3                |    |    | •  | •        |    |    |    |    |    |    |

| Default               | Х  | Х  | Х  | Х        | 0  | 0  | 0  | 0  | 0  | 0  |

| Functions             |    |    |    |          |    |    |    |    |    |    |

| CDS gain control      |    |    |    |          |    |    |    |    |    |    |

| Black loop gain boost |    |    |    |          |    |    | √  |    |    |    |

| Boost period          |    |    |    |          |    |    |    |    |    |    |

| PGA Gain              |    |    |    |          |    |    |    |    |    |    |

| Default               | Χ  | 0  | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  |

| Functions             |    |    |    |          |    |    |    |    |    |    |

| PGA gain              |    |    |    |          |    |    |    |    |    |    |

| Black Level           |    |    |    |          |    |    |    |    |    |    |

| Default               | Х  | Х  | Х  | 1        | 0  | 0  | 0  | 0  | 0  | 0  |

| Functions             |    |    |    |          |    |    |    |    |    |    |

| Black level           |    |    |    |          |    |    |    |    |    |    |

**Register Operations**

|                       |    |    |    |    | Cor | itrol |    |    |    |    | Onevetions                              |

|-----------------------|----|----|----|----|-----|-------|----|----|----|----|-----------------------------------------|

|                       | D9 | D8 | D7 | D6 | D5  | D4    | D3 | D2 | D1 | D0 | Operations                              |

| Mode 1                |    |    |    |    |     |       |    |    |    |    |                                         |

| DOLIT timing control  |    | 0  |    |    |     |       |    |    |    |    | DOUT synchronizes to ADCK               |

| DOUT timing control   |    | 1  |    |    |     |       |    |    |    |    | DOUT synchronizes to OUTCK              |

| OLITCK malarity       |    |    | 0  |    |     |       |    |    |    |    | DOUT changes at OUTCK rising edge       |

| OUTCK polarity        |    |    | 1  |    |     |       |    |    |    |    | DOUT changes at OUTCK falling edge      |

| ADOK I't-             |    |    |    | 0  |     |       |    |    |    |    | Normal operation as timing chart        |

| ADCK polarity         |    |    |    | 1  |     |       |    |    |    |    | ADCK clock inversion                    |

|                       |    |    |    |    | 0   | 0     |    |    |    |    | ADIN function OFF                       |

| ADIN connection       |    |    |    |    | 0   | 1     |    |    |    |    | ADIN signal to PGA                      |

|                       |    |    |    |    | 1   | х     |    |    |    |    | ADIN signal to ADC                      |

| December              |    |    |    |    |     |       | 0  |    |    |    | Reserved                                |

| Reserved              |    |    |    |    |     |       | 1  |    |    |    | Reserved                                |

| ADC output            |    |    |    |    |     |       |    | 0  |    |    | Normal operation, ADC data output       |

| ADC output            |    |    |    |    |     |       |    | 1  |    |    | ADC output high-Z, or logic of STBY     |

| Disch land word       |    |    |    |    |     |       |    |    | 0  |    | Normal operation                        |

| Black level reset     |    |    |    |    |     |       |    |    | 1  |    | Black level reset, or logic of RESET    |

| 5 .                   |    |    |    |    |     |       |    |    |    | 0  | Normal operation                        |

| Power down            |    |    |    |    |     |       |    |    |    | 1  | Power down, or logic of STBY            |

| Mode 2                |    |    |    |    |     |       |    |    |    |    |                                         |

| <u> </u>              |    |    | 0  |    |     |       |    |    |    |    | Normal clamp ±50μA                      |

| Clamp current         |    |    | 1  |    |     |       |    |    |    |    | Fast clamp ±100μA                       |

|                       |    |    |    | 0  |     |       |    |    |    |    | Clamp operation active for ADIN         |

| ADIN clamp            |    |    |    | 1  |     |       |    |    |    |    | No clamp for ADIN                       |

|                       |    |    |    |    | 0   | 0     |    |    |    |    | Normal mode, clamp both REFIN and CCDIN |

|                       |    |    |    |    | 0   | 1     |    |    |    |    | Clamp REFIN only                        |

| Clamp target          |    |    |    |    | 1   | 0     |    |    |    |    | Clamp CCDIN only                        |

|                       |    |    |    |    | 1   | 1     |    |    |    |    | Clamp off                               |

|                       |    |    |    |    |     |       | 0  | 0  |    |    | Normal operation as timing chart        |

|                       |    |    |    |    |     |       | 0  | 1  |    |    | S/H control polarity inversion          |

| S/H, enable logic     |    |    |    |    |     |       | 1  | 0  |    |    | Enable control polarity inversion       |

|                       |    |    |    |    |     |       | 1  | 1  |    |    | Both of S/H and enable inversion        |

|                       |    |    |    |    |     |       |    |    | 0  | 0  | Monitor off                             |

|                       |    |    |    |    |     |       |    |    | 0  | 1  | CDS signal to monitor                   |

| Monitor selection     |    |    |    |    |     |       |    |    | 1  | 0  | PGA output monitor                      |

|                       |    |    |    |    |     |       |    |    | 1  | 1  | Output REFIN and CCDIN                  |

| Mode 3                |    |    |    |    |     |       |    |    |    |    |                                         |

|                       |    |    |    |    | 0   | 0     |    |    |    |    | CDS gain=odB                            |

|                       |    |    |    |    | 0   | 1     |    |    |    |    | CDS gain=6.02dB                         |

| CDS gain control      |    |    |    |    | 1   | 0     |    |    |    |    | CDS gain=12.04dB                        |

|                       |    |    |    |    | 1   | 1     |    |    |    |    | CDS gain=–1.94dB                        |

|                       |    |    |    |    |     |       | 0  |    |    |    | Boost control on                        |

| Black loop gain boost |    |    |    |    |     |       | 1  |    |    |    | Always high gain                        |

|              |    |    |    |    | Cor | itrol |    |    |    |    | Omerations                |  |  |

|--------------|----|----|----|----|-----|-------|----|----|----|----|---------------------------|--|--|

|              | D9 | D8 | D7 | D6 | D5  | D4    | D3 | D2 | D1 | D0 | Operations                |  |  |

|              |    |    |    |    |     |       | 0  | 0  | 0  | 0  | Always low gain           |  |  |

|              |    |    |    |    |     |       | 0  | 0  | 0  | 1  | High gain for 1 OBP pulse |  |  |

|              |    |    |    |    |     |       | 0  | 0  | 1  | 0  | High gain for 2 OBP pulse |  |  |

| Deact named  |    |    |    |    |     |       | 0  | 0  | 1  | 1  | High gain for 3 OBP pulse |  |  |

| Boost period |    |    |    |    |     |       | 0  | 1  | 0  | 0  | High gain for 4 OBP pulse |  |  |

|              |    |    |    |    |     |       | 0  | 1  | 0  | 1  | High gain for 5 OBP pulse |  |  |

|              |    |    |    |    |     |       | 0  | 1  | 1  | 0  | High gain for 6 OBP pulse |  |  |

|              |    |    |    |    |     |       | 0  | 1  | 1  | 1  | High gain for 7 OBP pulse |  |  |

|          |    |    |           |    | Cor | itrol    | <u> </u> |    |    |    |              |          |               |

|----------|----|----|-----------|----|-----|----------|----------|----|----|----|--------------|----------|---------------|

|          | D9 | D8 | <b>D7</b> | D6 | D5  | D4       | D3       | D2 | D1 | D0 | Decimal      | HEX      | PGA Gain (dB) |

|          | 0  | 0  | 0         | 0  | 0   | 0        | 0        | 0  | 0  | 0  | 0            | 0        | 0             |

|          | 0  | 0  | 0         | 0  | 0   | 0        | 0        | 0  | 0  | 1  | 1            | 1        | 0.046         |

|          | 0  | 0  | 0         | 0  | 0   | 0        | 0        | 0  | 1  | 0  | 2            | 2        | 0.093         |

|          | 0  | 0  | 0         | 0  | 0   | 0        | 0        | 0  | 1  | 1  | 3            | 3        | 0.142         |

|          | 0  | 0  | 0         | 0  | 0   | 0        | 0        | 1  | 0  | 0  | 4            | 4        | 0.187         |

|          |    |    |           |    | ,   | L        |          |    |    |    | $\downarrow$ | ↓        | $\downarrow$  |

|          | 0  | 0  | 0         | 1  | 1   | 1        | 1        | 1  | 1  | 0  | 62           | 3E       | 2.915         |

|          | 0  | 0  | 0         | 1  | 1   | 1        | 1        | 1  | 1  | 1  | 63           | 3F       | 2.962         |

|          | 0  | 0  | 1         | 0  | 0   | 0        | 0        | 0  | 0  | 0  | 64           | 40       | 3.011         |

|          | 0  | 0  | 1         | 0  | 0   | 0        | 0        | 0  | 0  | 1  | 65           | 41       | 3.056         |

|          |    |    |           |    | ,   | <b>↓</b> |          |    |    |    | $\downarrow$ | ↓        | $\downarrow$  |

|          | 0  | 0  | 1         | 1  | 1   | 1        | 1        | 1  | 1  | 1  | 127          | 7F       | 5.972         |

|          | 0  | 1  | 0         | 0  | 0   | 0        | 0        | 0  | 0  | 0  | 128          | 80       | 6.021         |

|          | 0  | 1  | 0         | 0  | 0   | 0        | 0        | 0  | 0  | 1  | 129          | 81       | 6.058         |

|          |    |    |           |    | ,   | ↓        |          |    |    |    | ↓            | ↓        | $\downarrow$  |

| PGA gain | 0  | 1  | 1         | 0  | 0   | 0        | 0        | 0  | 0  | 0  | 192          | C0       | 9.031         |

|          |    |    |           |    | ,   | L        |          |    |    |    | $\downarrow$ | <b>\</b> | $\downarrow$  |

|          | 0  | 1  | 1         | 1  | 1   | 1        | 1        | 1  | 1  | 1  | 255          | FF       | 11.994        |

|          | 1  | 0  | 0         | 0  | 0   | 0        | 0        | 0  | 0  | 0  | 256          | 100      | 12.041        |

|          | 1  | 0  | 0         | 0  | 0   | 0        | 0        | 0  | 0  | 1  | 257          | 101      | 12.087        |

|          |    |    |           |    | ,   | L        |          |    |    |    | $\downarrow$ | <b>\</b> | $\downarrow$  |

|          | 1  | 0  | 1         | 0  | 0   | 0        | 0        | 0  | 0  | 0  | 320          | 140      | 15.05         |

|          |    |    |           |    | ,   | L        |          |    |    |    | $\downarrow$ | <b>\</b> | $\downarrow$  |

|          | 1  | 0  | 1         | 1  | 1   | 1        | 1        | 1  | 1  | 1  | 383          | 17F      | 18.14         |

|          | 1  | 1  | 0         | 0  | 0   | 0        | 0        | 0  | 0  | 0  | 384          | 180      | 18.061        |

|          | 1  | 1  | 0         | 0  | 0   | 0        | 0        | 0  | 0  | 1  | 385          | 181      | 18.108        |

|          |    |    |           |    |     | ↓ _      |          |    |    |    | $\downarrow$ | ↓        | $\downarrow$  |

|          | 1  | 1  | 1         | 0  | 0   | 0        | 0        | 0  | 0  | 0  | 448          | 1C0      | 21.071        |

|          |    |    |           |    | ,   | ļ        |          |    |    |    | <b>\</b>     | <b>\</b> | <b>\</b>      |

|          | 1  | 1  | 1         | 1  | 1   | 1        | 1        | 1  | 1  | 0  | 510          | 1FE      | 23.987        |

|          | 1  | 1  | 1         | 1  | 1   | 1        | 1        | 1  | 1  | 1  | 511          | 1FF      | 24.032        |

|             | Operation, ADC Code |    |    |          |    | ode |              |    | Black Code |    |           |           |

|-------------|---------------------|----|----|----------|----|-----|--------------|----|------------|----|-----------|-----------|

|             | D9                  | D8 | D7 | D6       | D5 | D4  | D3           | D2 | D1         | D0 | Decimal   | HEX       |

| Black level |                     |    |    | 0        | 0  | 0   | 0            | 0  | 0          | 0  | Forbidden | Forbidden |

|             |                     |    |    | 0        | 0  | 0   | 0            | 0  | 0          | 1  | 1         | 1         |

|             |                     |    |    | <b>\</b> |    |     |              |    |            |    | <b>\</b>  | <b>\</b>  |

|             |                     |    |    | 0        | 0  | 0   | 1            | 1  | 1          | 1  | 15        | F         |

|             |                     |    |    | 0        | 0  | 1   | 0            | 0  | 0          | 0  | 16        | 10        |

|             |                     |    |    | 0        | 0  | 1   | 0            | 0  | 0          | 1  | 17        | 11        |

|             |                     |    |    | 0        | 0  | 1   | 0            | 0  | 1          | 0  | 18        | 12        |

|             |                     |    |    | 0        | 0  | 1   | 0            | 0  | 1          | 1  | 19        | 13        |

|             |                     |    |    |          |    |     | $\downarrow$ |    |            |    | <b>\</b>  | <b>\</b>  |

|             |                     |    |    | 0        | 1  | 0   | 0            | 0  | 0          | 0  | 32        | 20        |

|             |                     |    |    |          |    |     | $\downarrow$ |    |            |    | <b>\</b>  | <b>\</b>  |

|             |                     |    |    | 1        | 0  | 0   | 0            | 0  | 0          | 0  | 64        | 40        |

|             |                     |    |    | <b>\</b> |    |     |              |    |            |    | <b>\</b>  | <b>\</b>  |

|             |                     |    |    | 1        | 1  | 1   | 1            | 1  | 0          | 0  | 124       | 7C        |

|             |                     |    |    | 1        | 1  | 1   | 1            | 1  | 0          | 1  | 125       | 7D        |

|             |                     |    |    | 1        | 1  | 1   | 1            | 1  | 1          | 0  | 126       | 7E        |

|             |                     |    |    | 1        | 1  | 1   | 1            | 1  | 1          | 1  | 127       | 7F        |

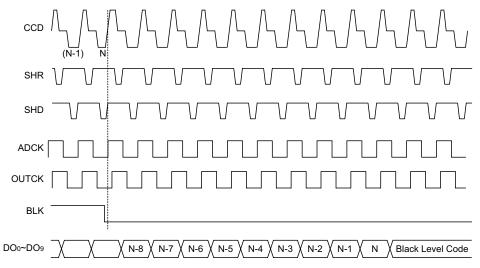

# **Timing Diagrams**

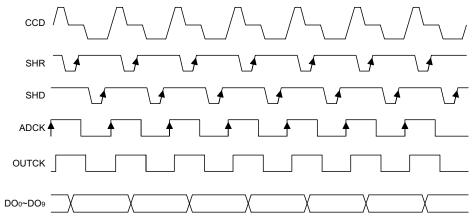

# AD Conversion Timing (at ADIN (ADC) Input Mode 1 Register D5=1)

**ADC Direct Input Chart**

These figures are shown when the Mode 1 D8 bit is set to "1", and an external clock is input to the OUTCK pin. When setting D8 bit to "0", the ADCK is used as OUTCK.

Note: At default condition in ADIN mode, data are sampled at the falling edge of the ADCK clock, and are output at the rising edge of the OUTCK clock. Set the ADCK polarity register to "1" when the data are sampled and are output at the falling edge of the ADCK clock.

The diagram on the upper portion of this page shows the default timing and the lower left figure shows the inverted timing.

Delay from data sampling to data output

ADCK normal: At Mode 1 register D6=0; 5.5 clk delay

ADCK inversion: At Mode 1 register D6=1; 6.0 clk delay

In ADIN input mode, the above mentioned register setting is available.

At ADIN (PGA) input Mode 1 register D5=0 and D4=1, digital data output is delayed by 2 clks.

#### **ADCK Clock Waveform**

# **Control Interface Timing**

V<sub>SS</sub>=0V, Ta=25°C)

| Cumahal          | Parameter                   |      | est Conditions | Min.  | Tirm | Max. | I I as i 4 |

|------------------|-----------------------------|------|----------------|-------|------|------|------------|

| Symbol           | Parameter                   | VDD  | Conditions     | WIII. | Тур. | wax. | Unit       |

| S <sub>CYC</sub> | SCK Clock Frequency         | 3.0V | _              | _     | _    | 10   | MHz        |

| S <sub>LO</sub>  | SCK Clock Low Level Width   | 3.0V | _              | 40    | _    | _    | ns         |

| S <sub>HI</sub>  | SCK Clock High Level Width  | 3.0V | _              | 40    | _    | _    | ns         |

| S <sub>SU</sub>  | Data Setup Time Period      | 3.0V | _              | 20    | _    | _    | ns         |

| S <sub>H</sub>   | Data hold Time Period       | 3.0V | _              | 20    | _    | _    | ns         |

| S <sub>R</sub>   | SCK, CS Rising Time Period  | 3.0V | 30%→70%        | _     | _    | 6    | ns         |

| S <sub>F</sub>   | SCK, CS Falling Time Period | 3.0V | 70%→30%        | _     | _    | 6    | ns         |

| SNUM             | Number of Serial Data       | 3.0V | _              | _     | 16   | _    | pcs        |

Serial I/F Timing Chart

# **Data Output Sequence**

Pixel Data Readout Sequence (1): Start of Conversion

Pixel Data Readout Sequence (2): End of Conversion

# **Clock Timing Variations by Register Setting**

Clock timing variations when it is inverted by register settings.

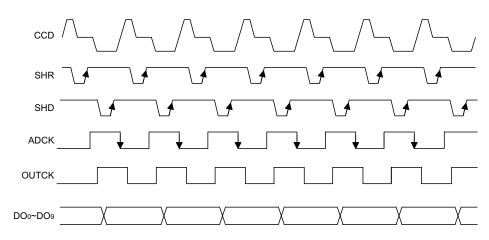

# • No inversion

Mode 1 register D6=0, Mode 2 register D2=0; Default

Pulse Control (Default: No Inversion)

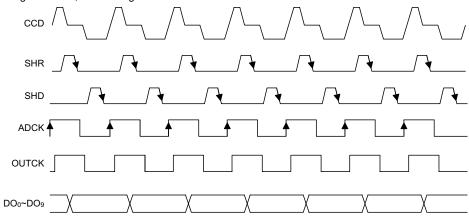

# • ADCK inversion

Mode 1 register D6=1, Mode 2 register D2=0

**Pulse Control (ADCK Inversion)**

# • SHR & SHD inversion

Mode 1 register D6=0, Mode 2 register D2=1

Pulse Control (SHR & SHD Inversion)

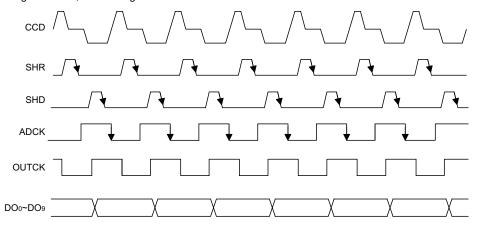

# • ADCK, SHR & SHD inversion

Mode 1 register D6=1, Mode 2 register D2=1

Pulse Control (ADCK, SHR & SHD Inversion)

# **Application Circuits**

Note: "\*" Pin 18 can also connect to ground with a  $4.7k\Omega$  resistor.

"\*\*" The capacitor connects to OBCAP pin maybe need adjust by user's applications from 0.1µF~1µF typically.

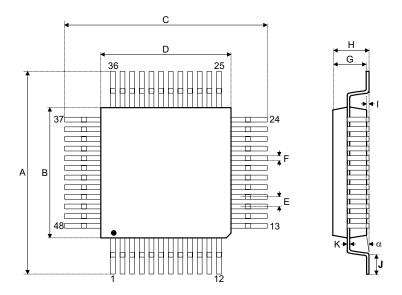

# **Package Information**

# 48-pin LQFP (7×7) Outline Dimensions

| Symbol | Dimensions in mm |      |            |  |  |  |  |  |

|--------|------------------|------|------------|--|--|--|--|--|

| Symbol | Min.             | Nom. | Max.       |  |  |  |  |  |

| Α      | 8.90             | _    | 9.10       |  |  |  |  |  |

| В      | 6.90             | _    | 7.10       |  |  |  |  |  |

| С      | 8.90             | _    | 9.10       |  |  |  |  |  |

| D      | 6.90             | _    | 7.10       |  |  |  |  |  |

| Е      | _                | 0.50 | _          |  |  |  |  |  |

| F      | _                | 0.20 | _          |  |  |  |  |  |

| G      | 1.35             | _    | 1.45       |  |  |  |  |  |

| Н      | _                | _    | 1.60       |  |  |  |  |  |

| I      | _                | 0.10 | _          |  |  |  |  |  |

| J      | 0.45             | _    | 0.75       |  |  |  |  |  |

| K      | 0.10             | _    | 0.20       |  |  |  |  |  |

| α      | 0°               | _    | <b>7</b> ° |  |  |  |  |  |

## Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

#### Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070

Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

# Holtek Semiconductor Inc. (Shanghai Sales Office)

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China 200233

Tel: 021-6485-5560 Fax: 021-6485-0313 http://www.holtek.com.cn

## Holtek Semiconductor Inc. (Shenzhen Sales Office)

43F, SEG Plaza, Shen Nan Zhong Road, Shenzhen, Ćhina 518031

Tel: 0755-8346-5589 Fax: 0755-8346-5590 ISDN: 0755-8346-5591

## Holtek Semiconductor Inc. (Beijing Sales Office)

Suite 1721, Jinyu Tower, A129 West Xuan Wu Men Street, Xicheng District, Beijing, China 100031

Tel: 010-6641-0030, 6641-7751, 6641-7752

Fax: 010-6641-0125

#### Holmate Semiconductor, Inc. (North America Sales Office)

46712 Fremont Blvd., Fremont, CA 94538

Tel: 510-252-9880 Fax: 510-252-9885 http://www.holmate.com

### Copyright © 2004 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.